==============================================================================

@

2002/10/10(22:33:51)[題]:新 200LX(2MB) の 128MB

化。

------------------------------------------------------------------------------

【プロローグ】

3年前に究極の 128MB な LX

が、FHPPC 9番会議室に発表された時は、全く解らないけど凄いなぁ〜。と思っていました。

LX で 128MB

が可能だと分かっただけで満足していました。

当時 DRAM

メモリーやドライバもないし、まして回路も動作原理も理解できないし、駆動時間も短いので作ったとしても自分には利用用途が

ないな〜と思っていました。

昨年あたりから DRAM

も入手できるようになり、9番会議室でもこのメモリーを使った改造が発表され、私も手を染めていきました。

そこへ今年の6月、C-kuma さんの 128MB

成功の報告が上がり、地図データでCドライブも目一杯なこともあり、一度は私も 128M

を作って

みたいなと想うようになりました。

3年前の当時のログを紐解いてみると何となくできそうな気がして、ドライバが入手できたら試してみたいと思うようになりました。

手始めに 2MB ドータ基板を流用して1バンク 32MB を作り、その後ドライバ (Times2

Teck) も入手できたこともあり、オンボード 64MB 化しま

した。そしてやっと 128MB 化に成功しました。

(^^)

自分には無理と思っていたのですが、まさか究極の 128MB 化まで手を染めるとは思ってもみませんでした。

(^^;;;

私でも 128MB 化できたのは、9番会議室の 5080 発言

を基に回路を作り、一連のツリーを参考にさせていただいたおかげです。

目新しさはありませんが、配線板を流用したことでだいぶ楽できたと思っています。(^^)

【作業のアウトライン】

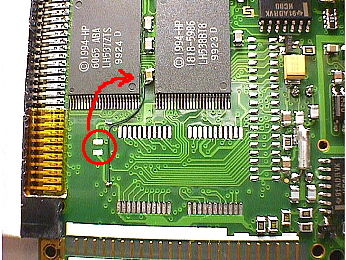

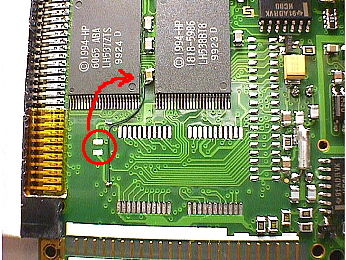

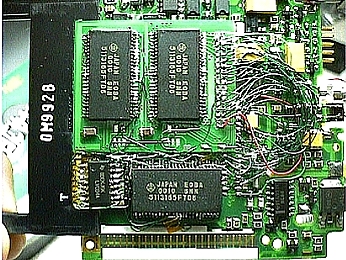

1.新 200LX(2MB) の既存 DRAM を剥がし、パスコンも

ROM の隙間に移動する。DRAM跡地に 13165 を亀4段にし、アドレス変換回

路(SN74LVC00) をPCカードピンの間だに設置して

64MB をチェック。

2.FHPPC-Tuned32M 配線板を流用して、それぞれ亀2段にして 64MB 基板とする。

3.|CAS 遅延回路

(SN74LVC04) を変換回路の上に乗せて固定。

4.倍速で RAM TEST をし、128MB

をパスすることを確認。運が良ければ爆速でも通るかも。

【DRAM 配置】

┏━━━━━━━━━┓ ┏━━━━━━━━━┓┏━━━━━━━━━┓

┃ 4 ┃ ┃ 6 ┃┃ 8 ┃

┠─────B───┨ ┠─────C───┨┠─────D───┨

┃ 3 ┃ ┃ 5 ┃┃ 7 ┃

┣━━━━━━━━━┫┏━┻━━━━━━━━━┻┻━━━━━━━━━┻━┓

┃ 2 ┃┃ FHPPC−Tuned32M配線板 ┃

┠─────A───┨┗━┳━━━━━━━━━━━━━━━━━━━━┳━┛

┃ 1 ┃ ┃ ROM ┃

━━┻━━━━━━━━━┻━━┻━━━━━━━━━━━━━━━━━━━━┻━━

既存ランド

1〜8が DRAM で、A〜Dのペアがバンク0〜3に対応。

配線は既存ランド上に4段重ねのA,B。 FHPPC-Tuned32M 配線板を流用して2段重ねのC,Dを ROM 上に配し、ソケットランドから配線を取る。

【変換回路】

HITACHI HM5113165FTD6×8

TI SN74LVC00ANS(4xNAND)×1 DRAM A B C D

⌒ ⌒ ⌒ ⌒

a11 >─┬───────────┬──────────> A11 1 2 3 4 5 6 7 8

│ │

│ │

│ └──────────> |OE0 1 3 5 7

│

│ 1┌┤ ̄ ̄\ 3

├──┤| 1 )o─┬───────────> |OE1 2 4 6 8

│ 2└┤__/ │ 9

│ └──┤ ̄ ̄\ 8

│ | 3 )o───> |WE0 1 3 5 7

│ ┌──┤__/

│ 4┌┤ ̄ ̄\ 6 │ 10

|we >─-)──┤│ 2 )o─┤

│ 5└┤__/ │ 12

│ └──┤ ̄ ̄\11

│ | 4 )o───> |WE1 2 4 6 8

└─────────────┤__/

13

【遅延回路】

TI SN74LVC04ANS(6xINV)×1

1│\ 2 3│\ 4

|lcas>-───────┤04>o───┤04>o─────>|LCAS 1 2 3 4 5 6 7 8

│/ │/

5│\ 6 13│\ 12

|ucas>-───────┤04>o───┤04>o─────>|UCAS 1 2 3 4 5 6 7 8

│/ │/

【FHPPC-Tuned32M 引き出し線】

│

│

■ ■━━━→ |RAS3 ■ ■━━━→ |RAS2 │

マザーソケットランド マザーソケットランド │

■ ■ ■ ■ ■ ■ │

┃ ジャンパ ┃ a11 a10 │

┗━━━━━━━━━━━━┛ ┌─┐ ┏━┓ ┏━┓ │

FHPPC-Tuned32M Board └─┘ ┗┳┛ ┗┳┛ │

─────────────────────────╂───╂──┘

a11←━━━━━━━━┛ ┃

a10←━━━━━━━━━━━━┛

FHPPC-Tuned32M 基板の 36 ピンランドからの当該信号線は、マザー基板のソケットランドへジャンパ配線する。

【配線ポンチ絵】

|LCAS

┌───────────────────────────────────-┐

│┌─────────────────────────────────-┐│

★││|lcas Vcc |UCAS HM5113165FTD6×8 ││

↑││ LVC04×1 ↑ ↑ +-------------U------------+ ││

│││ 1┌─-U-─┐14│ │┌─-1┏|━━┓VCC VSS┏━━|┓50─┐││

││└─┤1A Vcc├─┘ ││ ┗|━━┛vcc vss┗━━|┛ │││

││ 2│ │13 ││ 2┏|━━┓D0 D15┏━━|┓49 │││

││┌─┤1Y 6A├──┐││ ┗|━━┛d0 d15┗━━|┛ │││

│││ 3│ │12 │││ 3┏|━━┓D1 D14┏━━|┓48 │││

││└─┤2A 6Y├──-)┘│ ┗|━━┛d1 d14┗━━|┛ │││

││ 4│ │11 │ │ 4┏|━━┓D2 D13┏━━|┓47 │││

│└──┤2Y 5A├─┐│ │ ┗|━━┛d2 d13┗━━|┛ │││

│ 5│ │10││ │ 5┏|━━┓D3 D12┏━━|┓46 │││

└───┤3A 5Y├ ││ │ ┗|━━┛d3 d12┗━━|┛ │││

6│ │9 ││ │ 6┏|━━┓VCC VSS┏━━|┓45 │││

┌──┤3Y 4A├─┤│ │ ┗|━━┛vcc vss┗━━|┛ │││

│ 7│ │8 ││ │ 7┏|━━┓D4 D11┏━━|┓44 │││

│┌─┤GND 4Y├ ││ │ ┗|━━┛d4 d11┗━━|┛ │││

││ └────┘ ││ │ 8┏|━━┓D5 D10┏━━|┓43 │││

│├────────┘│ │ ┗|━━┛d5 d10┗━━|┛ │││

└-)─────────┘ │ 9┏|━━┓D6 D9┏━━|┓42 │││

│ │ ┗|━━┛d6 d9┗━━|┛ │││

↓ │ 10┏|━━┓D7 D8┏━━|┓41 │││

vss │ ┗|━━┛d7 d8┗━━|┛ │││

│ 11┌|──┐NC 折 折 NC┌──|┐40 │││

Hornet↑ │ └|──┘ └──|┘ │││

|RAS1(126Pin)B│ └─12┌|──┐VCC VSS┌──|┐39─┘││

│ |WE0 └|──┘ └──|┘ ││

│ ┌─────-13┌|──┐|WE |LCAS┌──|┐38──-)┘

│ │ ┌-─┘└|──┘ └──|┘ ┌─┘★

└──)───-)─-14┌|──┐|RAS |UCAS┌──|┐37│┌─┘

│ |WE1│┌-┘└|──┘ └──|┘ ││|OE0

│ ││ 15┌|──┐NC 折 |OE┌──|┐36-)-)┐

└──┐││A └|──┘nc nc└──|┘ └)-)-)┐

│││ 16┌|──┐NC 折 折 NC┌──|┐35││││

│││ └|──┘nc |lcas└──|┴─┘│││

|we │││ 17┌|──┐NC 折 折 NC┌──|┐34 │││

┌────────────-)-)-)-─┴|──┘|we |ucas└──|┴──┘││

│ │││ 18┌|──┐NC 折 折 NC┌──|┐33 ││

│ ││└─-┴|──┘|ras0 |oe└──|┘ ││

│ Hornet |a10>───┐││ 19┌|──┐A0──┐ A11┌──|┬───┤│

│ (133Pin) │││ └|──┘nc └──-a9└──|┘ ││

│ │││ 20┌|──┐A1──┐ A10┌──|┐31─┐││

│ │││ └|──┘nc └──-a8└──|┘ │││

│ │││ 21┏|━━┓A2 A9┏━━|┓30 │││

│ Hornet |a11>──┐│││ ┗|━━┛a0 a7┗━━|┛ │││

│ (132Pin) ││││ 22┏|━━┓A3 A8┏━━|┓29 │││

│ ││││ ┗|━━┛a1 a6┗━━|┛ │││

│ ┌────────┤│││ 23┏|━━┓A4 A7┏━━|┓28 │││

│ │ vcc││││ ┗|━━┛a2 a5┗━━|┛ │││

│ │ ↑││││ 24┏|━━┓A5 A6┏━━|┓27 │││

│ │ LVC00×1 │││││ ┗|━━┛a3 a4┗━━|┛ │││

│ │ 1┌────┐│││││ 25┏|━━┓VCC VSS┏━━|┓26 │││

│ ├─┤1A VCC├┘││││ ┗|━━┛vcc vss┗━━|┛ │││

│ │ 2│ │13││││ +---------------------------+ │││

│ └─┤1B 4B├─┤└-)-)─────────────────────┘││

│ 3│ │12└─-)-)──────────────────────┘│

│┌──┤1Y 4A├──┐││ │

││ 4│ │11 │││ │

└-)┬─┤2A 4Y├──-)-)┘ │

││ 5│ │10 ││ ┏━━━┓:ランドに亀半田付けする足 │

│└─┤2B 3B├──┤│ ┗━━━┛ │

│ 6│ │9 ││ ┌───┐:ランドから引き出す線 │

│┌─┤2Y 3A├──┼-)─┐ ──┴───┘ │

││ 7│ │8 ││ │ ──┬───┐:DRAM ピンから引き出す線 │

││┌┤GND 3Y├──-)┘ │ └───┘ │

│││└────┘ │ │ │

││└──→ vss │ │ │

│└─────────┘ │ |OE1 │

└─────────────┴──────────────────────┘

※上図ピン足に付記した数値とアルファベットは、下段の数値&小文字アルファベットは既存 RAM のピン足を示し、 上段の数値&大文字アルファベットは

亀にした 5113165,6FTD6 のピン足を示す。また亀の NC な足は全て折る。

接続は上の配線ポンチ絵に従う。 相変わらずセンスが無く、見づらいですが汲み取っていただければ幸いです。

ロジック IC は LVC を使いましたが、ALVC や VCX を使えばより安定した高速動作が期待できる...かも。

【作業手順】

1.既存 DRAM を取り除き、パスコンを ROM の隙間に移動する。

2.まずは亀4段にして 64MB

化します。NC Pin は全て折り、|WE(16Pin),|OE(36Pin) を水平に伸ばして亀にする。

3.PCカードピンとの間だに変換回路の

NAND(LVC00) を両面テープで固定し、配線ポンチ絵に従い配線する。

DRAM ペアBの|RAS はソケットランドの|ras3(29)

に配線する。

4.|WE0 はペアA,Bの DRAM1,3 に綱渡し配線。同様に|WE1 はペアA,Bの DRAM2,4

に綱渡し配線する。

5.|OE0 と|OE1 も同様にペアA,Bの DRAM1,3 と DRAM2,4 に綱渡しする。

6.19(A0) を

Hornet の|a10(133Pin) に配線、変換回路からの A11 も Hornet の|a11(132Pin)

に配線。

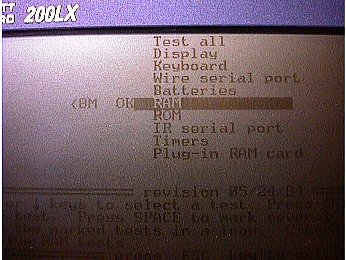

7.配線のチェック後、RAM TEST を行い、以下のように 64MB に成っていることを確認する。TEST

時間は約40分掛かります。

バンク : 0 1 2 3

カウント:D47 0 0

D47

容 量 :32M 0 0 32M

───────────────────

合 計

:64MB

亀4段での 64MB 化

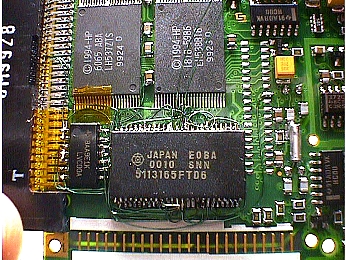

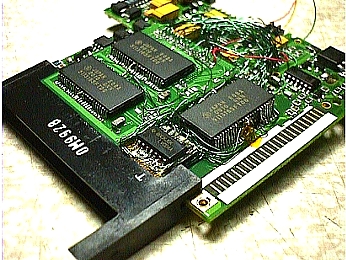

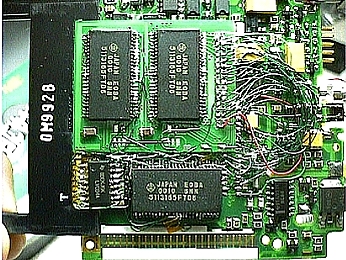

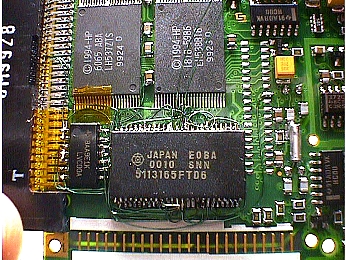

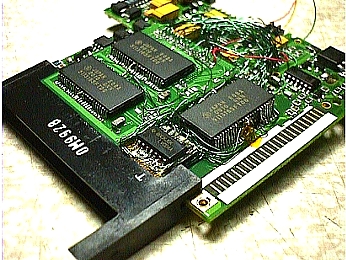

8.次に FHPPC-Tuned32M 配線板を流用して 64MB

基板にする。 まず配線板とタンタルコンの一部が干渉するのでヤスリで 1mm

程削り

ます。配線板裏を絶縁テープで覆う。またポンチ絵の所をジャンパし、パスコン2個を付ける。

9.3番で配線した|ras3(29)

を外し、直接 Hornet の|ras1(126Pin) に配線。

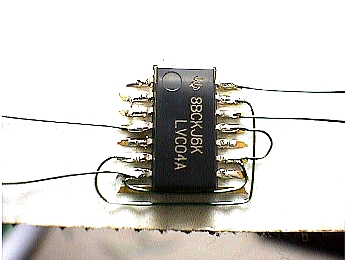

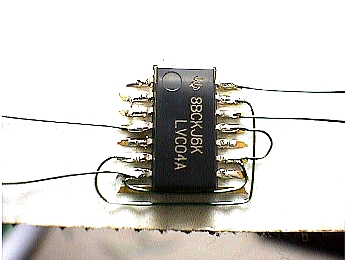

10.|CAS 遅延回路 (LVC04) を変換回路 (LVC00)

の上に乗せる。私は切れるシート基板の切れ端を使って 14Pin を半田付けしました。

ペアAの|#cas, と|#CAS の間に遅延回路の LVC04

を入れる。

LVC04 配線の様子

11.ペアC,Dの上段

DRAM6,8 の|WE1(13Pin) は水平に伸ばし、綱渡し配線で亀4段側の DRAM4 の|WE1 に配線。

12.ペアC,Dの|OE0

はそれぞれ綱渡し配線で DRAM5,7 とペアBの DRAM3 の|OE0 に配線。同様に DRAM6,8 の|OE1 はペアB DRAM4

の

|OE1 に綱渡し配線。

13.ペアC,Dの|#CAS は配線板のランド (6,30) から直接ペアBに配線。

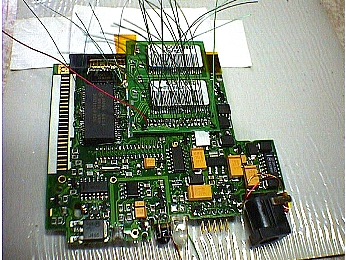

14.配線板の

a10,a11 は DRAM4 側に配線。

15.配線板のその他の信号線は全てマザー基板のソケットランドに配線。

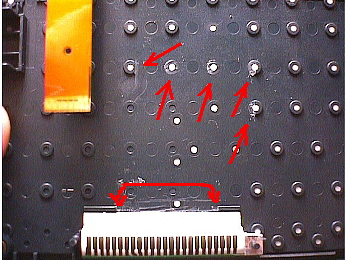

配線途中

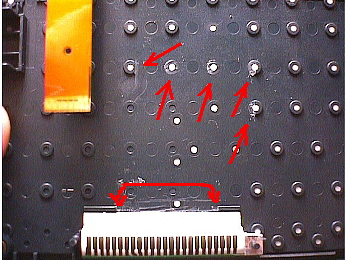

16.キーボード裏と DRAM

が当たる部分を削る。キーフレキ押さえの段差と、凸2個と凸3個を約半分削りました。

このままですとキーボードが少し膨らみます。彫刻刀などで地肌を削ればいいのですが、削りすぎに注意が必要です。

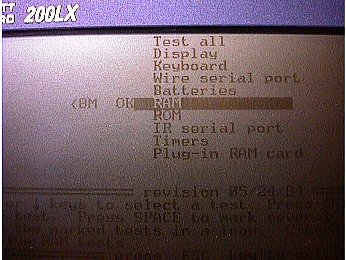

17.配線チェック後、RAM TEST

(約90分)を行い、128MB になることを確認して完成。

バンク : 0 1 2 3

カウント:D47

D47 D47 D47

容 量 :32M 32M

32M 32M

───────────────────

合 計 :128MB(<8M)

RAM TEST 結果表示

17.CONFIG.SYS にドライバ rdt2t.exe

を追加して立ち上がり時に y と答えれば、Fドライブとして 96MB が作られます。

Fドライブの chkdsk を行った画面

【結果】

新

200LX(128MB) FMODEM倍速。爆速では RAM3 の後半でこけます。 (/_;)

RAM TEST:90分 フルバンク D47 で合計

128MB(C=32MB,F=96MB)

サスペンド電流:5.80mA (2.602V) (デジマル)

定常時:40mA (アナログ)

アプリ起動時:170mA (アナログ)

ファイルコピー:260mA (アナログ)

以上、PCカードは入れていません。また電源昇圧もしていません。

(爆速化するつもりで遅延回路(LVC04)を付けましたが、倍速では付けなくても

RAM TEST は通っていました)

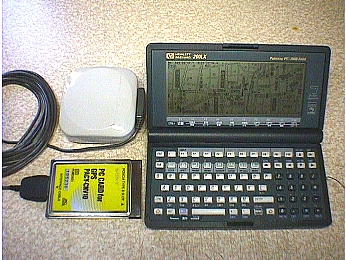

通信(XJ3144)、LAN転送(EN2216-1)、GPS(PACYNV-10) で使えています。 10日間ほど使って今のところOKです。 (^^)

フラッシュ(220MB)

入れてハードウェアバイブルに同梱されていた BATTSIM で自動運転テストを行った結果、 駆動時間(BATTLOG)

は平均

9時間 (1900mAh NiMH) 程度でした。

高容量になるとどうしても消費電力が大きくなり、LX

のメリットの一つが失われてしまい、電池の保ちとのトレードオフを考えるとあまりお奨め

はできませんが、使用目的を限定すれば 128MB も十分に有用性はあると思います。電池切れに注意すれば常用 LX

としても使えそうです。

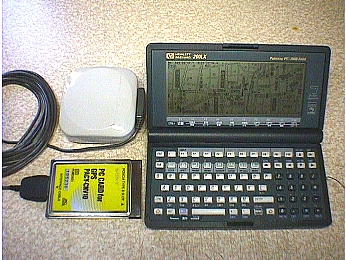

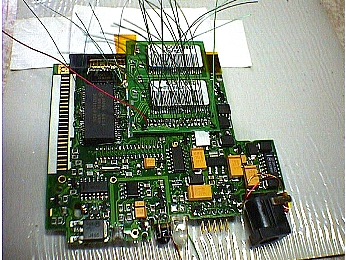

全体の画像 マザー基板を上から見た画像

マザー基板を横から見た画像

GPS受信機とLX

【感想】

はじめ、ROM 上の DRAM

を手配線しようとチマチマ始めたのですが、気力が萎えて途中でメゲました。 (^^;;;

残しておいたチューンド32M配線板は使いたくなかったのですが、手を出してしまいました。

でも流用したことで配線量は少なくて済みました。(^^)

私の場合、これまで 32MB 機に GPS

用の切り出し地図データを入れていて、容量を圧迫するため2年程遠のいていたのですが、

SONY PACYNV-10 と DMAPLX

でカーナビや登山でGPS 専用マシンが出来上がりました。(^^)

私でも曲がりなりに完成することが出来たのは、FHPPC

9番会議室の蓄積された情報や、多数の達人の方々のおかげです。

この場をお借りして心から感謝いたします。

_(..)_

【エピローグ】

電池の持ちも、思ったより良さそうなので常用LX として使うことにしました。

(^^)

SURER サイトで最新版ドライバが公開されました。基本的にユーザーサポートが対象のようですので、取り扱いには注意が必要です。

とは云え、誰でも個人の責任において動作チェックに使えるのは嬉しいです。

今後

128MB キットが実現できれば改造工作も楽になると思います。ぜひ軌道に乗ることを期待している一人です。 o(^-^)o